焦点快播:铠侠和西部数据将展示300+层3D NAND闪存,进一步提高性能和密度

2023-05-05 22:39:35 来源: 超能网

【资料图】

【资料图】

2023年VLSI技术和电路研讨会将于2023年6月11至16日在日本京都举行,铠侠(Kioxia)和西部数据将展示最新的创新成果,以支持未来更高容量、更高性能的3D NAND存储设备。

据eeNewsEurope报道,铠侠和西部数据正在寻求实现8平面(eight-plane)的1Tb 3D TLC NAND闪存,具有超过210个活动层,接口速率达到了3.2 GT/s。这与今年3月推出的218层3DNAND闪存非常相似,密度为17Gb/mm^2,只不过从4平面变成了8平面,这一定程度上也增加了存储控制的复杂性,推高了开发和制造的成本,产品开发的时间也变长了。据称,其程序吞吐量为205 MB/s,读取延迟为40μs。

新的论文显示,铠侠是将1Tb 3D TLC NAND闪存X方向数据查询区域减少到41%,从而实现3.2 GT/s的接口速率,使得存储器和主机之间的数据传输速度更快。不过这种新的设计可能会导致线路拥塞,铠侠通过引入混合行地址解码器(X-DEC),以更有效地管理增加的布线密度,从而减少延迟。此外,铠侠还利用了一种单脉冲双选通技术,允许在单个脉冲内感测两个存储单元,将总感测时间减少了18%。

铠侠和西部数据还合作开发300+层的3D NAND闪存,计划采用金属诱导侧向结晶(MILC)技术,让开发人员能够在垂直储孔内创建单晶14微米长的“通心粉状”硅(Si)通道。在实验性的操作中,开发人员还利用了一种尖端的吸镍方法消除硅材料中的杂质和缺陷,从而提高了单元阵列的性能,而且在没有牺牲可靠性的情况下,读取噪音至少降低了40%,通道电导率提高了10倍。

标签:

[责任编辑:]

猜你喜欢

- (2023-05-05)【聚看点】对话《长江之歌》词作者胡宏伟:多次来武汉写下《大武汉》|面谈

- (2023-05-05)全球新消息丨火热五一档 电影市场迎来消费热潮

- (2023-05-05)进原材料的运费怎么做会计分录_运费怎么做会计分录 全球快资讯

- (2023-05-05)姚明老婆叶莉身高_姚明老婆

- (2023-05-05)【天天热闻】怎么删除页眉的横线2007_怎么删除页眉的横线

- (2023-05-05)当前简讯:万科企业:4月份实现合同销售金额334.7亿元

- (2023-05-05)微光星海

绿了盐碱地 建成新粮仓(人民眼·盐碱地综合利用

绿了盐碱地 建成新粮仓(人民眼·盐碱地综合利用

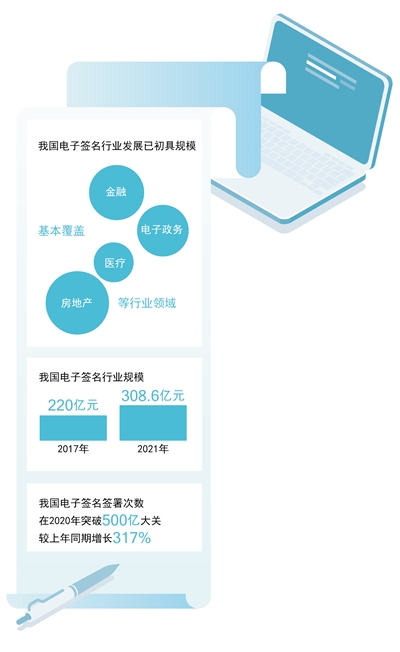

电子签名 方兴未艾(大数据观察·加快建设数字中

电子签名 方兴未艾(大数据观察·加快建设数字中